- Miércoles, 07 Septiembre 2011

La especificación Serial RapidIO Gen2 contiene mejoras significativas para las capas físicas, lógicas y de transacción. La especificación de la capa física ha acelerado al doble la velocidad por vía, alcanzando 6,25 Gbaudios; ha duplicado la distancia de transmisión objetivo a 100 cm de FR4 y dos conectores y, al mismo tiempo, ha reducido la tasa de bits erróneos (BER) en tres órdenes de magnitud (a 10-15).

La especificación Serial RapidIO Gen2 contiene mejoras significativas para las capas físicas, lógicas y de transacción. La especificación de la capa física ha acelerado al doble la velocidad por vía, alcanzando 6,25 Gbaudios; ha duplicado la distancia de transmisión objetivo a 100 cm de FR4 y dos conectores y, al mismo tiempo, ha reducido la tasa de bits erróneos (BER) en tres órdenes de magnitud (a 10-15).

En este artículo se detallan algunos métodos de diseño utilizados para desarrollar un tejido de conmutación digital Gen2 de 240 Gbps junto con serializadores y deserializadores (SerDes) analógicos y encapsulación de alta velocidad, a fin de cumplir los exigentes requisitos de rendimiento de la especificación Serial RapidIO Gen2; y para asegurar que los circuitos analógicos de alta velocidad no afectan al núcleo digital de alto rendimiento (o el converse) de los dispositivos Gen2. También se explican algunas implicaciones de uso resultantes de cambiar a SerDes con rendimiento Serial RapidIO Gen2.

Mejoras de la capa física Serial RapidIO Gen2

La especificación Gen2 de la capa física incluye nuevos anchos de vía de puerto de 2x, 8x y 16x para complementar los anchos de 1x y 4x de la especificación Gen 1. Muchos dispositivos de punto final y conmutadores disponibles en el mercado soportan puertos de 4x, 2x y 1x para hasta 20 Gb por segundo de caudal bruto, lo que supone más del doble de la capacidad de soluciones Ethernet de 10 Gb y supera PCI Express Gen2 en un 25%.

La especificación Serial RapidIO Gen2 cubre todas las especificaciones eléctricas clásicas para transmisores y receptores de corto, medio y largo alcance, incluyendo “máscaras de ojo” si procede. La especificación Gen 1 no requirió ecualización de ningún tipo, pero algunos proveedores optaron por implementar la ecualización. No obstante, la especificación Gen2 requiere una ecualización a 6,25 Gbaudios para cualquier alcance. A 5 Gbaudios, probablemente será necesaria para distancias largas, y es opcional para distancias cortas y medias. En caso de alcances largos de 6,25 Gbaudios, no se especifica ninguna máscara de ojo para el receptor, porque es posible que no haya ningún ojo al final del canal. Esto repercute sin duda en las posibilidades que tiene el usuario en el laboratorio para determinar la integridad de la señal vista en el dispositivo receptor.

La especificación Serial RapidIO no requiere generar ni comprobar patrones de SerDes (por ejemplo, transmitir un patrón de secuencia binaria pseudoaleatoria [PRBS] y comprobarlo en el receptor), pero algunos proveedores de dispositivos utilizan esta funcionalidad patentada. Una función de caracterización BER nueva en la especificación Serial RapidIO Gen2 es el contador de errores de decodificación 8b/10b por vía. Aunque no se pueden contar los errores multibit en un grupo de códigos determinado, los errores registrados a este nivel probablemente indicarían una línea gravemente degradada. En cambio, este contador es un indicador muy fiable de la BER real de líneas razonablemente eficaces con una BER de aproximadamente 10-9 o mejor.

La especificación Serial RapidIO no requiere generar ni comprobar patrones de SerDes (por ejemplo, transmitir un patrón de secuencia binaria pseudoaleatoria [PRBS] y comprobarlo en el receptor), pero algunos proveedores de dispositivos utilizan esta funcionalidad patentada. Una función de caracterización BER nueva en la especificación Serial RapidIO Gen2 es el contador de errores de decodificación 8b/10b por vía. Aunque no se pueden contar los errores multibit en un grupo de códigos determinado, los errores registrados a este nivel probablemente indicarían una línea gravemente degradada. En cambio, este contador es un indicador muy fiable de la BER real de líneas razonablemente eficaces con una BER de aproximadamente 10-9 o mejor.

SerDes: ecualización, indicador integrado ODS (On-Die Scope), pruebas BER

IDT, el proveedor líder de conmutadores Serial RapidIO, acaba de anunciar la disponibilidad de los conmutadores CPS-1848 y CPS-1616 de segunda generación (Gen2). Para cumplir las altas exigencias de la especificación Serial RapidIO Gen2, IDT ha diseñado un receptor de 6,25 Gbaudios que utiliza un ecualizador de tiempo continuo (CTE) y uno de decisión por realimentación (DFE).

El CTE proporciona un simple cero para aumentar la amplificación de la frecuencia relevante (es decir, la mitad de la tasa de baudios). Se trata de una amplificación activa, aunque se lleva a cabo de modo pasivo en todos los bits recibidos. Este impulso en una banda determinada mejora la ganancia de la señal recibida, a la vez que minimiza la ganancia de ruido.

Además, se utilizó un DFE de cinco derivaciones, que posibilita una ganancia muy selectiva y, al mismo tiempo, minimiza el ruido al impulsar las señales. El DFE sirve para compensar la interferencia entre símbolos (ISI), es decir, el impacto negativo que tienen los bits transmitidos previamente sobre cada bit nuevo. El DFE examina activamente el registro de bits transmitidos con anterioridad (en este caso, hasta cuatro bits anteriores) y realimenta una decisión, basada en este registro, sobre cómo impulsar cada bit. De este modo, el receptor puede eliminar el efecto de las frecuencias ISI, que, de lo contrario, interferirían con la siguiente señal entrante.

Se han desarrollado numerosas implementaciones y funciones de diseño para minimizar el consumo de energía. El transmisor, por ejemplo, ofrece un elevado grado de control de impulsión (fuerza del impulso y preénfasis). El usuario no tiene que cumplir los requisitos estándares en detrimento de la BER. En el receptor, un reloj a media velocidad permite considerables ahorros de energía. Esta arquitectura divide la ruta de datos recibidos en bits pares e impares y, a continuación, aprovecha al máximo un reloj que funciona a media velocidad. Efectivamente, la circuitería DFE también se ha diseñado para soportar esta arquitectura a media velocidad de reloj y de ruta de datos dividida. El DFE incluye funciones para minimizar el consumo energético, que permiten al usuario apagar las derivaciones no utilizadas.

Se han desarrollado numerosas implementaciones y funciones de diseño para minimizar el consumo de energía. El transmisor, por ejemplo, ofrece un elevado grado de control de impulsión (fuerza del impulso y preénfasis). El usuario no tiene que cumplir los requisitos estándares en detrimento de la BER. En el receptor, un reloj a media velocidad permite considerables ahorros de energía. Esta arquitectura divide la ruta de datos recibidos en bits pares e impares y, a continuación, aprovecha al máximo un reloj que funciona a media velocidad. Efectivamente, la circuitería DFE también se ha diseñado para soportar esta arquitectura a media velocidad de reloj y de ruta de datos dividida. El DFE incluye funciones para minimizar el consumo energético, que permiten al usuario apagar las derivaciones no utilizadas.

Para minimizar el ruido en el SerDes, se utilizaron condensadores de desacoplamiento para ocupar todo el espacio disponible en el chip a fin de reducir el ruido de los circuitos lógicos digitales. Asimismo, se empleó una distribución de reloj diferencial para el reloj de referencia en todos los bucles enganchados en fase (PLL) del dispositivo, además de los circuitos de estos PLL en cada vía. La distribución de reloj diferencial mejora la inmunidad al ruido del reloj. Adicionalmente, el aislamiento del SerDes se realizó separándolo físicamente del núcleo digital, y el ruido de conmutación digital se redujo al mínimo en la circuitería analógica.

Asegurar una adecuada señal de alta velocidad hasta el encapsulado

A 6,25 Gbaudios, el diseño y la ingeniería de canales son cada vez más importantes y están relacionados con el transceptor. De hecho, a esta velocidad, la especificación Serial RapidIO Gen2 remite a los transceptores y canales conformes a StatEye. Se puede diseñar un transceptor conforme a StatEye contra un modelo de canal conforme a StatEye y/o se puede diseñar un canal conforme a StatEye contra un modelo de transceptor conforme a StatEye. El canal y el transceptor son inseparables en cuanto al cumplimiento de las especificaciones.

Esto tiene ramificaciones hasta el diseño de encapsulados. IDT ha diseñado los encapsulados FCBGA (Flip Chip Ball Grid Array) para conmutadores que cumplen los requisitos de la especificación; el encapsulado, por sí mismo, forma parte del canal, y su diseño se realizó en coordinación con el propio chip, minimizando las longitudes de traza del BGA, formando cuidadosamente pares de vías y logrando su característica impedancia.

Para impedir que las señales transmitidas se unan con las vías del receptor, el CPS-1848 tiene pines de aislamiento de conexión a tierra entre los pines Tx y Rx (véase la figura 2). Además, los pines de la fuente de alimentación dividen cada vía para reducir el acoplamiento de una vía a la siguiente. La inductancia del bucle de alimentación/conexión a tierra se minimiza proporcionando voltaje Vdd de núcleo y conexión a tierra a modo de tablero de ajedrez. Así, es fácil aplicar condensadores de desacoplamiento en el lado secundario de la placa de circuito impreso.

Para impedir que las señales transmitidas se unan con las vías del receptor, el CPS-1848 tiene pines de aislamiento de conexión a tierra entre los pines Tx y Rx (véase la figura 2). Además, los pines de la fuente de alimentación dividen cada vía para reducir el acoplamiento de una vía a la siguiente. La inductancia del bucle de alimentación/conexión a tierra se minimiza proporcionando voltaje Vdd de núcleo y conexión a tierra a modo de tablero de ajedrez. Así, es fácil aplicar condensadores de desacoplamiento en el lado secundario de la placa de circuito impreso.

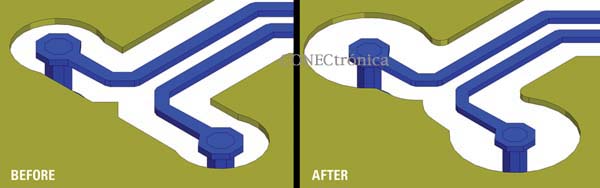

A fin de mejorar la señalización para las líneas Serial RapidIO de alta velocidad, se utilizan anti-pads de vía para despejar el pad de vía de la señal procedente del plano de tierra en la misma capa que el pad. Para eliminar la capacitancia excesiva, el despeje de anti-pads para el pad de la vía de láser aumenta de 50 µm a 100 µm, y para el pad de la vía del núcleo, de 100 µm a 150 µm (véase la figura 3), lo que puede mejorar, por ejemplo, la pérdida de retorno en 12,5 dB a 5,0 GHz.

Para minimizar el ruido procedente del núcleo digital en el SerDes de alta velocidad y los PLL, el dispositivo y el encapsulado separan los raíles de alimentación analógicos y los del núcleo. Según la hoja de datos del dispositivo, el diseñador de placas de circuito impreso debe mantener estos raíles separados. Una alimentación específica del transmisor SerDes (Vddtx) funciona a 1,2 V, aunque el dispositivo se ha fabricado con un proceso de núcleo de 1,0 V. Esta tensión de alimentación de 1,2 V asegura una fuerte impulsión de la transmisión para garantizar que se cumplan con creces las especificaciones del transmisor Serial RapidIO.

Reflexiones sobre el uso con este rendimiento

Como se ha dicho antes, en caso de transmisión de largo alcance a 6,25 Gbaudios, es posible que no haya ojo a donde apuntar en el receptor. Con estas velocidades de vía, normalmente se necesitarían unos osciloscopios cuyo coste asciende a 100.000 $ o más para comprobar la integridad de la señal. Además, la ecualización del receptor puede mejorar la señal que se ve en el receptor. En efecto, lo que el osciloscopio percibe como externo al dispositivo puede ser mucho peor que lo que percibe el propio chip, después de la ecualización. Con la ecualización del receptor, el ODS se convierte en una herramienta muy útil para ver lo que ve el dispositivo. Todos los conmutadores Gen2 de IDT utilizan un ODS por vía, que es independiente del patrón. Por eso funciona con cualquier patrón arbitrario, incluyendo los patrones de prueba PRBS-31 definidos en la especificación Serial RapidIO, así como el protocolo de tiempo de ejecución Serial RapidIO mientras los paquetes están atravesando los enlaces. El ODS es fantástico para optimizar rápidamente los parámetros de transmisión y recepción, incluidos los de ecualización, vigilando simplemente que haya una apertura de ojo óptima.

Un patrón de prueba PRBS-31 puede ser una manera idónea y estricta de caracterizar el canal, pero tiene un espectro de transición de bits más amplio de lo que se vería con el protocolo Serial RapidIO estándar durante el tiempo de ejecución. Como se ha dicho antes, la especificación Serial RapidIO no requiere generadores ni comprobadores de patrones PRBS. La BER de tiempo de ejecución en el sistema Serial RapidIO será más baja de lo que se vería mediante el patrón PRBS. Sin duda, la BER del sistema de tiempo de ejecución se determina mejor si se usan los contadores de errores de decodificación 8b/10b de Serial RapidIO Gen2.

Conclusión

Los dispositivos Serial RapidIO Gen2 duplican la velocidad de puerto a 20 Gbps, y están diseñados para las aplicaciones rigurosas de backplane de calidad de portadora (carrier-grade). Para lograr este rendimiento es clave el SerDes mejorado, que admite hasta 6,25 Gbaudios e incorpora un DFE y circuitos de ecualización adicionales. Los proveedores deben sincronizar los componentes analógicos y digitales de sus chips, así como el propio encapsulado, para asegurar que estas velocidades se cumplen sobradamente.

Con la doble velocidad de línea y la ecualización necesaria a estas velocidades, es posible que el usuario experimente un cambio de paradigma al usar estos dispositivos y en las características de los transceptores y canales. Nuevas funciones específicas de proveedor, tales como ODS y contadores BER estándares, servirán de ayuda en esta transición e, indiscutiblemente, contribuirán a facilitar el trabajo en el laboratorio en comparación con otros productos.

El autor

Trevor Hiatt ocupa el cargo de gerente de productos en la división IDT Communications. Entre sus funciones figuran la definición de productos estratégicos, la gestión de programas y el marketing para productos Serial RapidIO. Trevor es licenciado en Ingeniería Eléctrica e Informática por la Universidad de California de Santa Bárbara. Para más información, póngase en comtacto con Trevor Hiatt escribiendo a: Esta dirección de correo electrónico está siendo protegida contra los robots de spam. Necesita tener JavaScript habilitado para poder verlo.

Trevor Hiatt ocupa el cargo de gerente de productos en la división IDT Communications. Entre sus funciones figuran la definición de productos estratégicos, la gestión de programas y el marketing para productos Serial RapidIO. Trevor es licenciado en Ingeniería Eléctrica e Informática por la Universidad de California de Santa Bárbara. Para más información, póngase en comtacto con Trevor Hiatt escribiendo a: Esta dirección de correo electrónico está siendo protegida contra los robots de spam. Necesita tener JavaScript habilitado para poder verlo.

Cursos Técnicos y Seminarios

Centro de recursos técnicos sobre retos de la ciberseguridad

En el mundo interconectado de hoy en día, la necesidad de integrar la seguridad en el nivel ...

Webinars D-Link sobre formación TIC

D-Link ha anunciado su nueva temporada de sus D-Link Academy Webinars. Los temas de esta nueva ...

Curso básico de Fibra Óptica Gratuito

Aquí tienes todas las fichas del Curso básico de fibra óptica publicado en los primeros número de ...

Plataforma Inmersiva de e-Learning Keysight University

Keysight Technologies, Inc ha anunciado Keysight University, una ...

Nokia aborda la seguridad de las redes como parte de su programa de certificación 5G

Nokia ha anunciado hoy un nuevo curso y certificación 5G de nivel profesional dirigido a la ...