Du cloud computing aux véhicules autonomes, la demande en interfaces mémoire plus rapides s'accélère. Une caractéristique technologique révolutionnaire des interfaces rapides telles que la DDR5, la LPDDR5 et la GDDR6 est l'égalisation au niveau des récepteurs des puces mémoire, qui permet de récupérer les signaux dégradés lors de leur passage sur le circuit imprimé (PCB). Les ingénieurs en électronique doivent minimiser les risques de problèmes d'intégrité du signal dans la conception des bus mémoire, ce qui implique de pouvoir prédire la qualité du signal après égalisation, de prototyper le système et de tester ses performances.

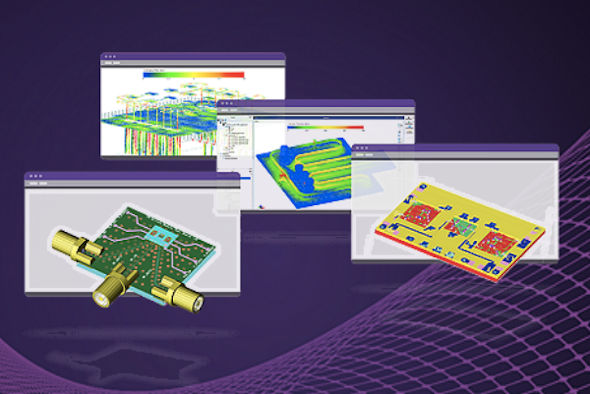

PathWave ADS 2022 de Keysight, un flux de travail pour la conception et le test de mémoires de nouvelle génération, permet aux ingénieurs matériels de respecter leurs délais de mise sur le marché et de fournir un produit final fiable et performant. Le concepteur de mémoire de PathWave ADS 2022 doit relever les défis de conception suivants :

- Modélisation précise du comportement de l'émetteur et du récepteur grâce à la génération de modèles de simulation avancés pour les émetteurs et les récepteurs DDR, avec égalisation flexible et entrées d'horloge externes.

- Optimisation des paramètres d'égalisation pour prédire les marges de conception grâce à un simulateur avancé qui utilise l'égalisation adaptative afin de trouver les paramètres optimaux pour une intégrité du signal optimale dans la liaison de données.

- Quantification de la marge dans le masque du diagramme de l'œil en prédisant de combien l'œil se fermera à différents taux d'erreur binaire (TEB) spécifiques à la norme, et en signalant la marge restante.

- Recherche des conditions de défaillance par exploration de la conception, en générant un lot de listes de simulation pour passer en revue tous les paramètres de conception possibles et en consignant les configurations réussies/échouées dans une feuille de calcul.

- Confiance dans la finalisation de la conception, de l'idée initiale aux tests, grâce à la production de rapports de conformité automatisés sur les formes d'onde simulées et à l'utilisation de méthodes de mesure cohérentes pour identifier les problèmes au plus tôt et tester efficacement les solutions potentielles.

« Le simulateur d'intégrité du signal de pointe PathWave ADS aide Xilinx dans le développement de nos systèmes de mémoire avancés. Notre collaboration avec Keysight nous permet d'optimiser les solutions de mémoire système pour nos clients », a déclaré Thomas To, directeur de l'intégration des systèmes de mémoire chez Xilinx.

« La DDR5 est une technologie révolutionnaire qui oblige les concepteurs à repenser leur stratégie de simulation et de mesure », a déclaré Brig Asay, directeur de la planification stratégique du groupe Infrastructure Internet chez Keysight. « L’expertise de Keysight en matière de DDR5, tant au niveau des techniques de simulation que de mesure, nous permet d’aider nos clients à relever les défis posés par cette technologie et de les guider vers la réussite de leurs conceptions dès la première itération. »

Des informations complémentaires sur PathWave ADS Memory Designer sont disponibles à l'adresse suivante :

- Événements de lancement de PathWave Design 2022

- Logiciel PathWave Design 2022

- PathWave ADS pour la conception numérique à haute vitesse