Actuellement, les modules HBM doivent être intégrés aux GPU car l'interconnexion électrique entre le GPU et la mémoire est limitée à quelques millimètres. Les prochaines générations de HBM nécessiteront des densités d'interconnexion de l'ordre de 10 Tbit/s/mm, voire plus. Les interconnexions optiques classiques, basées sur des VCSEL ou la photonique sur silicium (SiPh), promettent d'étendre la portée de l'interconnexion, mais peinent à répondre aux exigences en matière de taille, de densité de bande passante, de consommation, de latence, de température de fonctionnement et de coût. À l'inverse, les interconnexions LightBundle d'Avicenna, basées sur des microLED, offrent une densité de bande passante supérieure, une taille bien plus réduite, une consommation et une latence considérablement diminuées, ainsi qu'un coût très bas.

« Chez Avicena, nous sommes ravis de présenter l'émetteur-récepteur 1 Tbit/s le plus compact au monde, sous la forme d'un circuit intégré spécifique CMOS de 3 mm x 4 mm utilisant notre interface optique microLED exclusive », déclare Bardia Pezeshki, fondateur et PDG d'Avicena. « Tout le monde parle de solutions SiPh pour les applications de clusters d'IA. Cependant, pour les interconnexions à courte portée (moins de 10 m), nous pensons que notre solution à LED est intrinsèquement mieux adaptée grâce à sa taille compacte, sa densité de bande passante plus élevée, sa consommation et sa latence réduites, ainsi que sa tolérance à des températures allant jusqu'à 150 °C. ».

« La technologie d’interconnexion optique a le potentiel d’améliorer les performances entre les puces et en coulisses », déclare Marco Chisari, directeur du Centre d’innovation des semi-conducteurs de Samsung. « Avec une feuille de route visant une capacité de plusieurs Tbit/s et une efficacité énergétique inférieure au pJ/bit, les interconnexions LightBundle innovantes d’Avicenna peuvent permettre l’avènement d’une nouvelle ère d’innovation en IA, ouvrant la voie à des modèles encore plus performants et à un large éventail d’applications d’IA qui façonneront l’avenir. »

À propos de la technologie

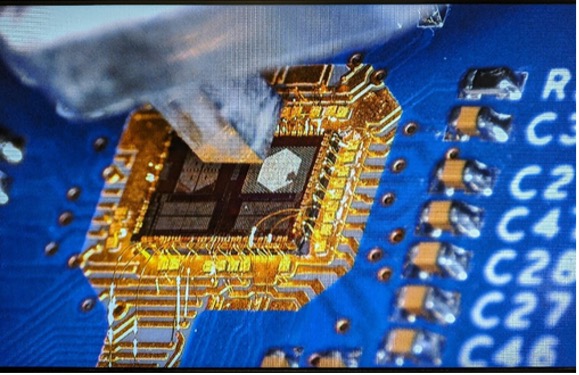

Les circuits intégrés hautes performances actuels utilisent des interfaces électriques de type SerDes pour atteindre une densité hors puce adéquate. Cependant, la consommation d'énergie et la bande passante de ces liaisons électriques se dégradent rapidement avec la longueur. Les technologies de communication optique conventionnelles, développées pour les applications réseau, se sont révélées impraticables pour les interconnexions entre processeurs et entre processeurs et mémoire, en raison de leur taille, de leur faible bande passante, de leur forte consommation d'énergie et de leur coût élevé. Le recours fréquent à des sources laser externes (ELS) avec SiPh accroît encore la complexité et le coût. À l'inverse, l'architecture d'interconnexion LightBundle™ repose sur des matrices de microLED GaN innovantes qui tirent parti de l'écosystème d'affichage microLED et peuvent être directement intégrées dans des circuits intégrés CMOS compacts et hautes performances. Ceci permet des E/S denses et basse consommation sur toute la surface du circuit intégré, autorisant des densités de puces sans précédent. Chaque matrice de microLED est connectée par un câble à fibre multicœur à une matrice correspondante de photodiodes compatibles CMOS.

« Nous avons déjà démontré la capacité de microLEDs à transmettre à plus de 10 Gbit/s par voie, ainsi que la faisabilité d'un ASIC de test gravé en CMOS 130 nm, fonctionnant sur 32 voies avec une consommation inférieure à 1 pJ/bit », explique Rob Kalman, cofondateur et directeur technique d'Avicenna. « Nous présentons aujourd'hui notre premier ASIC doté de plus de 300 voies et d'une bande passante agrégée de plus de 1 Tbit/s bidirectionnelle à 4 Gbit/s par voie. Cet ASIC, d'une surface inférieure à 12 mm², intègre un émetteur-récepteur complet, incluant les circuits pour les matrices optiques d'émission et de réception, ainsi qu'une interface électrique parallèle haut débit et diverses fonctions DFT/DFM telles que BERT, les boucles de retour et la surveillance de l'œil ouvert (OEM). Toutes les fonctionnalités clés de l'ASIC ont été validées et nous travaillons actuellement à l'amélioration de ses performances afin d'optimiser sa production. ».

La plateforme modulaire LightBundle permet des interconnexions à plusieurs dizaines de Tbit/s et une densité de débit supérieure à 10 Tbit/s/mm. Indépendante de tout procédé de fonderie, LightBundle s'intègre à une grande variété de nœuds de traitement de circuits intégrés. Sa compacité, sa haute densité, sa faible consommation et sa faible latence en font la solution idéale pour les interfaces de puces haute densité telles que UCIe, OpenHBI et BoW. Elle étend également considérablement la portée des interconnexions informatiques existantes, comme PCIe/CXL et les liaisons mémoire HBM/DDR/GDDR.