El CDR-TS-CM44013 de TeraSquare hace trizas el consumo del circuito integrado (CI) hasta 0,75W, en comparación con los niveles medios del CFP4 de 3,5W; no requiere una referencia de temporizador y tiene integrada capacidad de prueba JTOL, evitando el caro requisito de equipo de prueba externo.

El CDR-TS-CM44013 de TeraSquare hace trizas el consumo del circuito integrado (CI) hasta 0,75W, en comparación con los niveles medios del CFP4 de 3,5W; no requiere una referencia de temporizador y tiene integrada capacidad de prueba JTOL, evitando el caro requisito de equipo de prueba externo.

"Nuestro nuevo CI es verdaderamente revolucionario y estamos muy contentos de ser capaces de demostrarlo en el ECOC, donde ha estado presente por primera vez", comenta Dr.Jinho Park, CTO en TeraSquare.

“Es, por un margen considerable, la solución de consumo más baja que el mercado jamás ha visto y este requisito crítico es sólo una de las características principales que creemos que hace a nuestro nuevo desarrollo tan importante en todo el mundo."

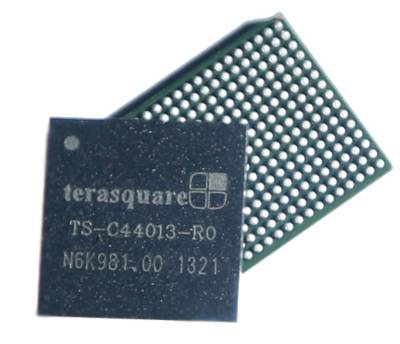

El CDR de 100 Gb/s en paralelo de TeraSquare tiene de 25.0 a 28.3Gb/s por canal en un encapsulado estándar BGA de 8 mm X 8 mm para módulos CFP4/QSFP28 y que soporta las especificaciones CEI-28G-VSR. No sólo es un CI innovador debido a su bajo consumo de energía, sino que cuenta con un modo sin referencia y funcionamiento con filtrado de jitter sin necesidad de condensador de filtro externo. El CI también incluye también capacidad de prueba integrada JTOL y generador PRBS, y fue demostrado en el stand de TeraSquare en la feria ECOC.

TeraSquare también presentó su segundo producto, un CDR de 100 Gb/s de conmutación inversa 10x10Gb/s y 4x25Gb/s que soporta plenamente OIF MLG1.0/MLG2.0 y CEI-28G-VSR para módulos CFP4/QSFP28. Este producto tiene todas las características del CDR de 100 Gb/s en paralelo de TeraSquare (TS- CM44013) y sólo consume 1.1W. Las primeras muestras estarán disponibles en Febrero de 2014.

Fundada en Diciembre de 2010, TeraSquare se esfuerza por ser una de las empresas líderes en el ámbito del diseño de CI Ethernet de 100 Gbps. Sin duda, un mercado muy prometedor en el futuro próximo, el diseño CI Ethernet de 100 Gbps es un campo desafiante que exige un alto nivel de competencia y capacidad que sólo un selecto grupo de proveedores aspirantes poseen. Con una demanda cada vez mayor de soluciones de Ethernet de alta velocidad en la industria de TI, TeraSquare se está preparando para cumplir con su objetivo de convertirse en el proveedor de CI Ethernet de alta velocidad, así como otros circuitos integrados de alta velocidad.

El Dr. Jinho Park cuenta con más de 10 años de experiencia en el diseño y producción en masa de CMOS de bajo consumo y alta velocidad. En su anterior cargo como Gerente de Diseño Senior de Marvell en el Silicon Valley, el Dr. Park construyó y dirigió un grupo de Investigación y Desarrollo de 30 doctores desarrolladores que alcanzaron el primer diseño analógico y de RF mundial de CI 802 11ac mobile MIMO. Con más de 40 patentes relacionadas con circuitos analógicos de alta velocidad y sistemas, a su nombre, el Dr. Park es la fuerza impulsora detrás de los diseños innovadores de TeraSquare en productos competitivos.

Más información o presupuesto