- Lunes, 13 Diciembre 2010

Las estaciones base inalámbricas de tercera y cuarta generación que utilizan los estándares de interfaz más comunes de hoy en día, tales como WCDMA, TD-SCDMA, LTE, TD-LTE y Wimax, necesitan una gran capacidad de procesamiento de señales para poder cumplir los requisitos de ancho de banda de los enlaces ascendentes y descendentes.

Las estaciones base inalámbricas de tercera y cuarta generación que utilizan los estándares de interfaz más comunes de hoy en día, tales como WCDMA, TD-SCDMA, LTE, TD-LTE y Wimax, necesitan una gran capacidad de procesamiento de señales para poder cumplir los requisitos de ancho de banda de los enlaces ascendentes y descendentes.

La primera arquitectura, que se muestra en la figura 1, utiliza uno o varios circuitos integrados de aplicación específica (ASIC) o matrices de puertas programables de campo (FPGA) para recibir y transmitir datos de antenas normalmente a través de la interfaz de radio pública común (CPRI) o por medio de la iniciativa de arquitectura abierta para estaciones base (OBSAI), un estándar de interfaz común para antenas. Éste se utiliza cuando la capa PHY (protocolo de la capa física) del protocolo inalámbrico se implementa en el/la ASIC/FPGA. A continuación, los datos se transfieren a través de S-RIO a un conjunto de procesadores digitales de señal (DSP) para el procesamiento del protocolo inalámbrico a nivel de la subcapa de control de acceso a medios (MAC). El procesamiento a nivel de la capa MAC superior se realiza en el procesador de control (CP). El CP se utiliza para la calidad de servicios (QoS) y numerosas funciones de gestión más en la tarjeta de banda base. Además, suele encargarse del acceso a la red a través de enlaces de Gigabit Ethernet así como de la implementación de la seguridad para el acceso a la red pública. Asimismo, en algunas arquitecturas se presenta una interfaz de red centralizada en la que el CP de cada tarjeta de banda base se puede comunicar con la tarjeta de interfaz de red en la que se ejecutará la función de seguridad para el acceso a la red pública.

Al utilizar una FPGA en esta arquitectura, la estación base es totalmente escalable y programable con software. Se puede describir como estación base configurable con software. Los diseñadores de sistemas tendrían la opción de aumentar o disminuir el tamaño de la FPGA así como la de añadir o quitar DSP para obtener una estación base de mayor o menor tamaño, capaz de atender a un número mayor o menor de abonados. Asimismo, para el algoritmo MIMO, los diseñadores podrían agrupar a los usuarios en grupos más grandes o más reducidos, lo que requeriría una mayor o menor capacidad de procesamiento de la FPGA y de los DSP.

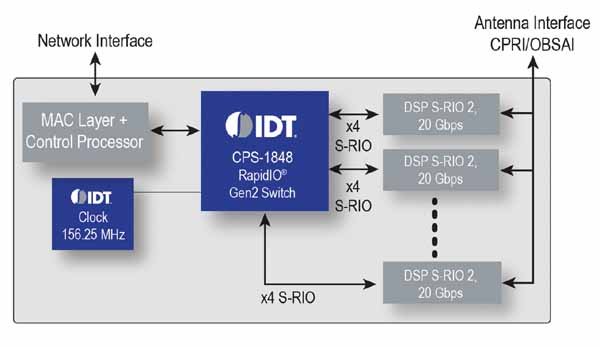

E n la segunda arquitectura, que se muestra en la figura 2, no se utiliza ni FPGA ni ASIC en la ruta de datos de antenas; en lugar de ello, todo el tráfico de antenas se envía a todos los DSP en el sistema. Esta es una arquitectura distribuida. Cada DSP recibe los datos de antenas y solamente utiliza lo que necesita para atender a los usuarios de su responsabilidad. Una vez finalizado el procesamiento de muestras en los DSP, los paquetes de datos pueden enviarse a través de S-RIO al procesador de control desde y hacia la red. De modo similar, hay mucho tráfico de control entre el procesador de control y el DSP para las funciones QoS y de gestión correspondientes a cada usuario. Serial RapidIO es ideal en arquitecturas que utilizan funciones de capas lógicas, tales como transacciones de memoria directas y/o RapidIO Messaging, que es una manera eficaz de transmitir mensajes largos de hasta 4 Kbs. La función RapidIO Messaging es una arquitectura de “empuje” (push) y presenta el sistema con la latencia más baja en comparación con otros protocolos. La latencia de conmutación de Serial RapidIO es igualmente mínima –más o menos 100 ns–, y establece una transferencia eficaz entre los procesadores digitales de señal. Además, esta arquitectura es escalable y también se puede describir como estación base configurable con software.

n la segunda arquitectura, que se muestra en la figura 2, no se utiliza ni FPGA ni ASIC en la ruta de datos de antenas; en lugar de ello, todo el tráfico de antenas se envía a todos los DSP en el sistema. Esta es una arquitectura distribuida. Cada DSP recibe los datos de antenas y solamente utiliza lo que necesita para atender a los usuarios de su responsabilidad. Una vez finalizado el procesamiento de muestras en los DSP, los paquetes de datos pueden enviarse a través de S-RIO al procesador de control desde y hacia la red. De modo similar, hay mucho tráfico de control entre el procesador de control y el DSP para las funciones QoS y de gestión correspondientes a cada usuario. Serial RapidIO es ideal en arquitecturas que utilizan funciones de capas lógicas, tales como transacciones de memoria directas y/o RapidIO Messaging, que es una manera eficaz de transmitir mensajes largos de hasta 4 Kbs. La función RapidIO Messaging es una arquitectura de “empuje” (push) y presenta el sistema con la latencia más baja en comparación con otros protocolos. La latencia de conmutación de Serial RapidIO es igualmente mínima –más o menos 100 ns–, y establece una transferencia eficaz entre los procesadores digitales de señal. Además, esta arquitectura es escalable y también se puede describir como estación base configurable con software.

En esta arquitectura, los diseñadores no solamente pueden definir estaciones base de tamaño mayor o menor para atender a más o menos usuarios, sino que también están en condiciones de cumplir diferentes estándares inalámbricos con la misma arquitectura. Basta con cambiar el software para convertir la arquitectura en una plataforma común entre diferentes estándares.

En las arquitecturas mostradas en las figuras 1 y 2, los flujos de datos de S-RIO difieren mucho. De modo similar, la misma arquitectura que cumpliría distintos estándares inalámbricos, tales como WCDMA y LTE, requeriría un flujo de datos

S-RIO diferente. Por esta razón, convendría modelar escenarios de tráfico S-RIO dentro del sistema para asegurar que la velocidad y el tamaño de cada enlace sean adecuados para ejecutar el algoritmo necesario sin excederse del tiempo presupuestado para cada estándar. S-RIO ofrece, respectivamente, anchos y velocidades de enlace x1, x2 y x4 y de 1,25 a 6,25 Gbps. Las figuras 1 y 2 muestran enlaces S-RIO x4, pero algunos sistemas pueden funcionar con enlaces más estrechos, si procede, de acuerdo con el número de usuarios atendidos y las características de cada DSP implicado.

Serial RapidIO es la única tecnología de interconexión definida para un conjunto distribuido de procesadores organizados en cualquier topología con fácil enrutamiento y adaptabilidad. Su enfoque simplista para enrutar paquetes, basado en el campo de identificación de destino, permite a los implementadores de software descubrir fácilmente nuevos nodos en un sistema o redistribuir el tráfico en caso de errores de procesamiento. Serial RapidIO es escalable y, al mismo tiempo, mantiene el mismo modelo de programación de software sin que haya los problemas de mapeo de memoria habituales en otros protocolos. Ningún otro protocolo puede convertir las dos arquitecturas, descritas arriba, en estaciones base programables con software.

Serial RapidIO es la única tecnología de interconexión definida para un conjunto distribuido de procesadores organizados en cualquier topología con fácil enrutamiento y adaptabilidad. Su enfoque simplista para enrutar paquetes, basado en el campo de identificación de destino, permite a los implementadores de software descubrir fácilmente nuevos nodos en un sistema o redistribuir el tráfico en caso de errores de procesamiento. Serial RapidIO es escalable y, al mismo tiempo, mantiene el mismo modelo de programación de software sin que haya los problemas de mapeo de memoria habituales en otros protocolos. Ningún otro protocolo puede convertir las dos arquitecturas, descritas arriba, en estaciones base programables con software.

Autor: Stephane Gagnon, Director de Gestión de Productos de Serial RapidIO, IDT

Acerca del autor

Stephane Gagnon, director de Gestión de Productos, se incorporó a IDT en agosto de 2000. Stephane desempeñó muchos cargos diferentes, entre ellos arquitecto de sistemas, director de Ingeniería de Sistemas y Pruebas de Fabricación y director de Marketing Estratégico. Durante los últimos diez años, Stephane también ha colaborado con el Grupo de Trabajo Técnico dedicado a RapidIO de la Asociación Profesional. Actualmente, preside el Comité Directivo de la Asociación Profesional. Antes de incorporarse a IDT, Stephane trabajó un año como ingeniero de aplicaciones (FAE) en Motorola, y siete años como diseñador de sistemas de hardware en Nortel Networks.