EINFÜHRUNG

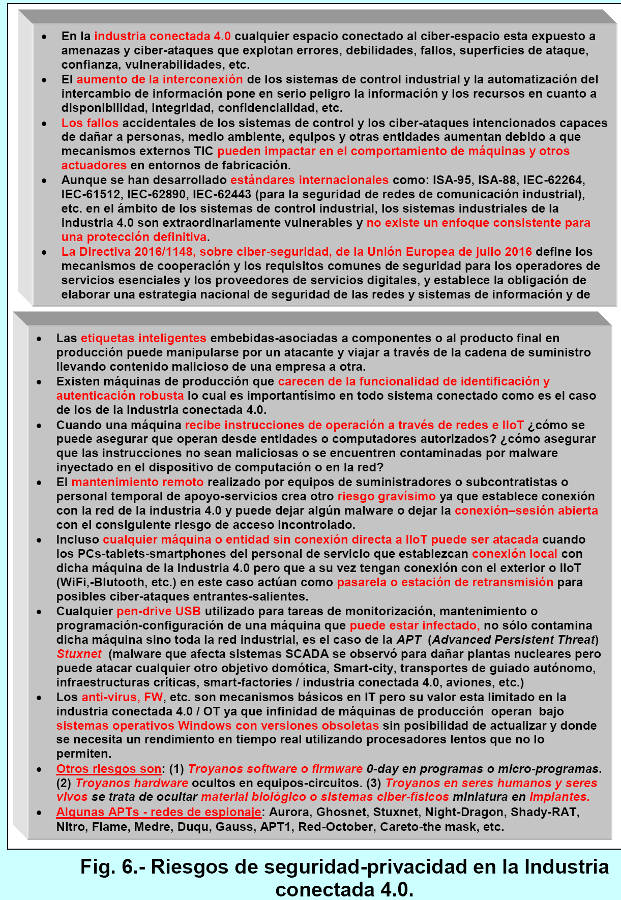

Das Konzept von Industrie 4.0 bezeichnet cyber-physische Produktionssysteme, die Ausführungssysteme mit Analyse- und Planungsfunktionen integrieren. Es steht für eine neue Art der Organisation von Produktionsressourcen durch die Implementierung intelligenter Fabriken, die an aktuelle Produktionsbedürfnisse und -prozesse angepasst sind, sowie durch Ressourcenoptimierung. Industrie 4.0 bietet zahlreiche Vorteile, wie die Vernetzung und Interoperabilität von Elementen durch das industrielle Internet der Dinge (IIoT), die digitale Transformation, Sensorüberwachung und Datenaggregation, die Unterstützung kontinuierlicher Verbesserung, dezentrale Entscheidungsfindung und gesteigerte Produktivität. Dieses ideale Szenario birgt jedoch in Verbindung mit der Vernetzung von Industrie 4.0 auch Schwachstellen, die zu vielfältigen Cyberangriffen führen können. Die Prävention von Cyberangriffen, die die Sicherheit und den Datenschutz von Produktionsanlagen und -daten gefährden, hat höchste Priorität. Es ist offensichtlich, dass jedes Industrie-4.0-Ökosystem Cybersicherheit und Datenschutz unterliegen muss. Innerhalb dieses Ökosystems lassen sich verschiedene Bereiche identifizieren: (1) Im Zentrum stehen die Fabriken der Zukunft und Fabrikcluster. Auf der grundlegendsten Ebene finden sich additive Fertigung mit 3D-Druckern (massive Individualisierung, Rapid Prototyping usw.), fortschrittliche Materialien und Nanotechnologie (Konnektivität, intelligenter Mehrwert für Produkte usw.), Robotik (autonome Produktivität in Echtzeit, vollständige Transparenz), Mechatronik (Mechanik mit Kybernetikintegration) sowie autonome Land- und Luftfahrzeuge (geringere Kosten, optimierter Workflow). Auf einer höheren Ebene stehen Sensoren und Aktoren (Rückverfolgbarkeit, Vorhersagefähigkeiten) und fortschrittliche Fertigungssysteme (cyber-physische Systeme, vollautomatische numerische Steuerung, M2M-Kommunikation und vollständig vernetzte Systeme). Eine weitere Ebene bilden Cloud Computing und Big Data/Analytics (Förderung von Kreativität, kollaborativer Fertigung usw.). (2) Die Interaktion mit Cloud Computing umfasst die externsten Cybersicherheits- und Datenschutzdienste (technologische Produkte mit längeren Lebenszyklen, besserer Schutz für IIoT-basierte Fertigung). (3) Die Interaktion mit den Anlagen der Zukunft umfasst Lieferantencluster, Logistik 4.0 (vollständig integrierte Lieferkette, umfassende Koordination, vernetzte Systeme), Kunden mit IIoT (Echtzeit-Datenerfassung, optimierte Lagerbestände, Objektkennzeichnung, Abfallreduzierung, Objekt-Internet-Kommunikation mittels energiesparender RFID-Technologie mit und ohne Chips, Bluetooth, ZigBee, UWB usw.) und Mass Customization (Flexibilität, bedarfsgerechte Fertigung, perfekte Ausrichtung auf Kundenbedürfnisse, effiziente Massenproduktion, verbesserte Kundeninteraktion im Marketing usw.). (4) Die Interaktion mit den Anlagen der Zukunft offenbart die Ressourcen der Zukunft (Windkraftanlagen, Solaranlagen, Geothermie, Gezeitenenergie usw. sind erneuerbare und saubere Energien und überall verfügbar).

Das Konzept von Industrie 4.0 bezeichnet cyber-physische Produktionssysteme, die Ausführungssysteme mit Analyse- und Planungsfunktionen integrieren. Es steht für eine neue Art der Organisation von Produktionsressourcen durch die Implementierung intelligenter Fabriken, die an aktuelle Produktionsbedürfnisse und -prozesse angepasst sind, sowie durch Ressourcenoptimierung. Industrie 4.0 bietet zahlreiche Vorteile, wie die Vernetzung und Interoperabilität von Elementen durch das industrielle Internet der Dinge (IIoT), die digitale Transformation, Sensorüberwachung und Datenaggregation, die Unterstützung kontinuierlicher Verbesserung, dezentrale Entscheidungsfindung und gesteigerte Produktivität. Dieses ideale Szenario birgt jedoch in Verbindung mit der Vernetzung von Industrie 4.0 auch Schwachstellen, die zu vielfältigen Cyberangriffen führen können. Die Prävention von Cyberangriffen, die die Sicherheit und den Datenschutz von Produktionsanlagen und -daten gefährden, hat höchste Priorität. Es ist offensichtlich, dass jedes Industrie-4.0-Ökosystem Cybersicherheit und Datenschutz unterliegen muss. Innerhalb dieses Ökosystems lassen sich verschiedene Bereiche identifizieren: (1) Im Zentrum stehen die Fabriken der Zukunft und Fabrikcluster. Auf der grundlegendsten Ebene finden sich additive Fertigung mit 3D-Druckern (massive Individualisierung, Rapid Prototyping usw.), fortschrittliche Materialien und Nanotechnologie (Konnektivität, intelligenter Mehrwert für Produkte usw.), Robotik (autonome Produktivität in Echtzeit, vollständige Transparenz), Mechatronik (Mechanik mit Kybernetikintegration) sowie autonome Land- und Luftfahrzeuge (geringere Kosten, optimierter Workflow). Auf einer höheren Ebene stehen Sensoren und Aktoren (Rückverfolgbarkeit, Vorhersagefähigkeiten) und fortschrittliche Fertigungssysteme (cyber-physische Systeme, vollautomatische numerische Steuerung, M2M-Kommunikation und vollständig vernetzte Systeme). Eine weitere Ebene bilden Cloud Computing und Big Data/Analytics (Förderung von Kreativität, kollaborativer Fertigung usw.). (2) Die Interaktion mit Cloud Computing umfasst die externsten Cybersicherheits- und Datenschutzdienste (technologische Produkte mit längeren Lebenszyklen, besserer Schutz für IIoT-basierte Fertigung). (3) Die Interaktion mit den Anlagen der Zukunft umfasst Lieferantencluster, Logistik 4.0 (vollständig integrierte Lieferkette, umfassende Koordination, vernetzte Systeme), Kunden mit IIoT (Echtzeit-Datenerfassung, optimierte Lagerbestände, Objektkennzeichnung, Abfallreduzierung, Objekt-Internet-Kommunikation mittels energiesparender RFID-Technologie mit und ohne Chips, Bluetooth, ZigBee, UWB usw.) und Mass Customization (Flexibilität, bedarfsgerechte Fertigung, perfekte Ausrichtung auf Kundenbedürfnisse, effiziente Massenproduktion, verbesserte Kundeninteraktion im Marketing usw.). (4) Die Interaktion mit den Anlagen der Zukunft offenbart die Ressourcen der Zukunft (Windkraftanlagen, Solaranlagen, Geothermie, Gezeitenenergie usw. sind erneuerbare und saubere Energien und überall verfügbar).

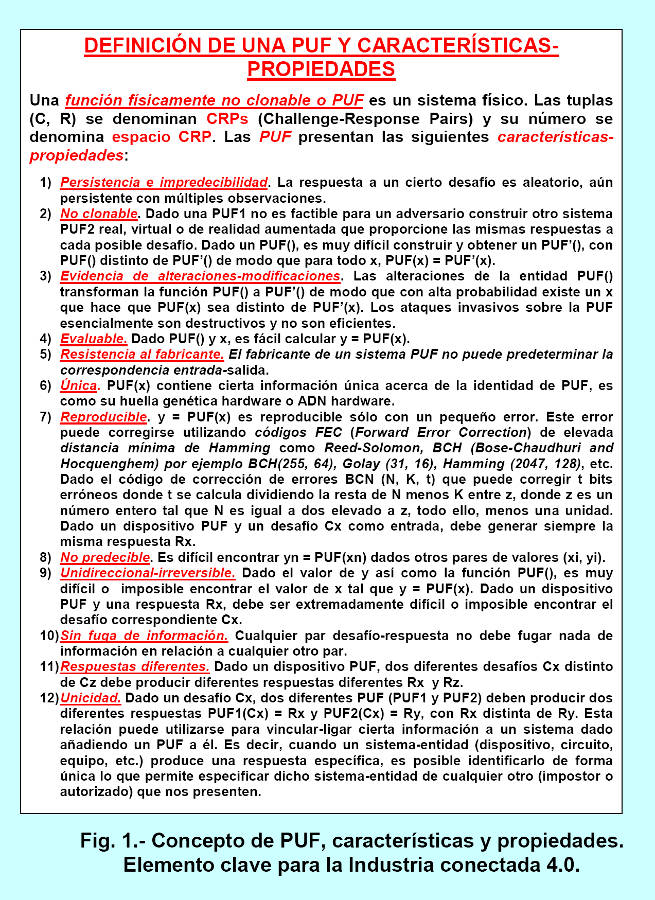

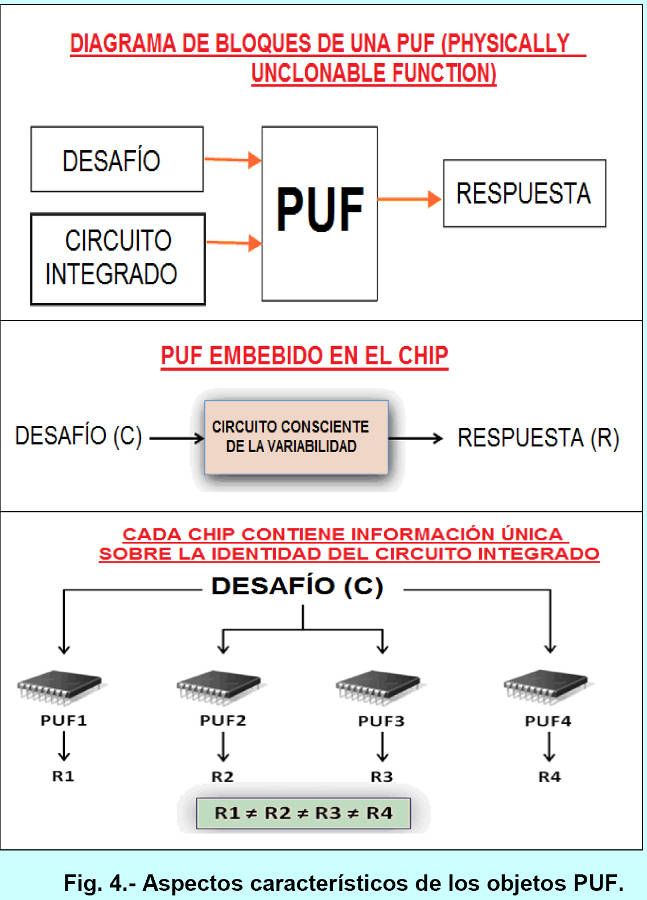

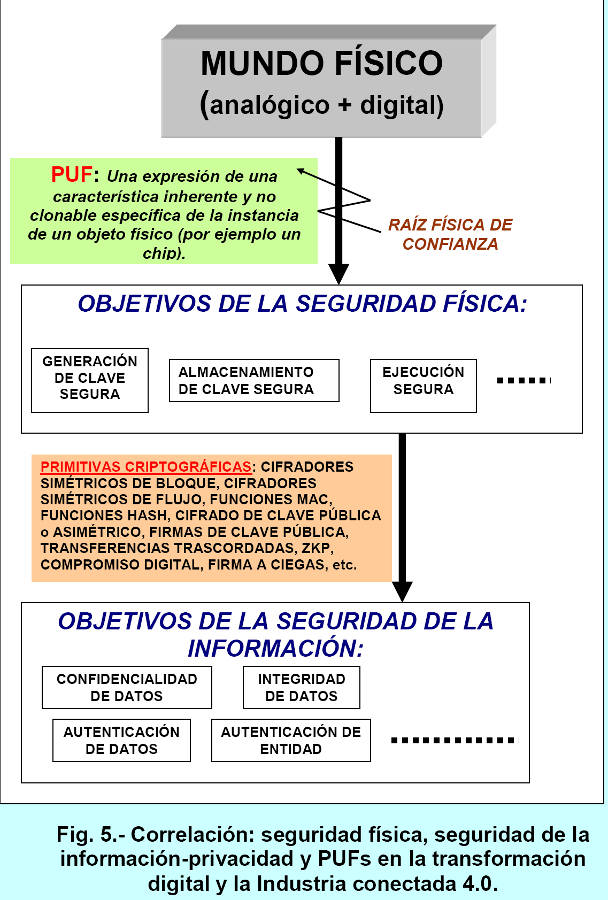

Diese Energie lässt sich speichern und stellt eine Alternative zu herkömmlichen Materialien wie Kohle dar. Eine Schlüsselkomponente für die Sicherheit und den Datenschutz von Industrie-4.0-Ökosystemen ist die PUF (Positive Function Unit). Eine PUF ist eine in ein physisches Objekt, wie beispielsweise einen Chip oder einen integrierten Schaltkreis, eingebettete Funktion. Bei einer Anfrage mit einer Challenge z generiert die PUF eine Antwort w, die sowohl von der Challenge z als auch von den einzigartigen analog-digitalen physikalischen Eigenschaften des Geräts und des Materials, das die PUF enthält, abhängt (d. h. von der einzigartigen internen Struktur der PUF, die durch zufällige Fertigungstoleranzen verursacht wird; diese Toleranzen sind in der Regel nicht reproduzierbar und liegen außerhalb der Kontrolle des PUF-Herstellers). Da PUFs durch Umwelteinflüsse bedingten Störungen unterliegen, liefern sie bei wiederholter Anfrage mit derselben Challenge leicht unterschiedliche Antworten. Dies lässt sich jedoch durch den Einsatz von FEC-Technologie (Fire Error Correction) mit einer sehr hohen Hamming-Distanz kompensieren. PUF-Architekturen (Publicly Identified Facility) werden auf einer Vielzahl von Plattformen implementiert, darunter FPGAs (Field-Programmable Gate Arrays), ASICs (Application-Specific Integrated Circuits), COTS-Produkte (Commercial Off-The-Shelf), Mikrocontroller, DSPs (Digital Signal Processors), ASSPs (Application-Specific Standard Products), SoCs (System-on-Chip), GPUs (Graphics Processing Units), ARM (Advanced RISC Machines), Mikroprozessoren und weitere. Innerhalb einer einzigen Plattform können unterschiedliche Technologien, wie beispielsweise CMOS-Knoten verschiedener Größenordnungen, zum Einsatz kommen. PUFs führen den Ansatz des „elektronischen Fingerabdrucks“ ein, wodurch die Identifizierung von den Eigenschaften des Geräts abhängt und nicht mehr auf einem geheimen Wissen beruht. Die moderne Informationssicherheit offenbart zunehmend ihre vielfältigen Facetten, wodurch ein stetig wachsendes Spektrum an Aufgaben bewältigt werden muss. Neben der herkömmlichen Kryptografie, die die Sicherheit von Daten gewährleistet, die in einem Netzwerk gespeichert oder übertragen werden, muss moderne Sicherheit einer wachsenden Zahl weiterer Anforderungen gerecht werden, wie etwa Vertrauen, Anonymität und die Vertraulichkeit von Handlungen. Frühe kryptografische Mechanismen, Protokolle und Methoden wurden für physisch gut geschützte Geräte entwickelt. Heutzutage ist jedoch die große Mehrheit der Geräte (RFID-/NFC-Tags mit und ohne Chips, intelligente Knoten in drahtlosen Sensornetzwerken (WSNs), Tablets usw.) leicht zugänglich, physisch ungeschützt und kann sich sogar in rauen Umgebungen befinden. Daher müssen moderne Sicherheitsprimitive (wie PUFs) gegen alle Arten von physischen Angriffen und Seitenkanalangriffen resistent sein und zudem kostengünstig und energieeffizient sein sowie die Einschränkungen tragbarer Computer und mobiler Kommunikationsgeräte mit begrenzter Akkukapazität und leistungsschwachen CPUs erfüllen. Die intrinsische Hardware-Sicherheit ist ein relativ neues Forschungsgebiet, das sich mit der sicheren Speicherung geheimer Schlüssel befasst. Die Generierung geheimer Schlüssel aus den intrinsischen Eigenschaften von Silizium, beispielsweise intrinsischen PUFs, erfordert keine dauerhafte Speicherung geheimer Schlüssel und der Schlüssel ist nur für eine minimale Zeitspanne im Bauelement vorhanden.

Diese Energie lässt sich speichern und stellt eine Alternative zu herkömmlichen Materialien wie Kohle dar. Eine Schlüsselkomponente für die Sicherheit und den Datenschutz von Industrie-4.0-Ökosystemen ist die PUF (Positive Function Unit). Eine PUF ist eine in ein physisches Objekt, wie beispielsweise einen Chip oder einen integrierten Schaltkreis, eingebettete Funktion. Bei einer Anfrage mit einer Challenge z generiert die PUF eine Antwort w, die sowohl von der Challenge z als auch von den einzigartigen analog-digitalen physikalischen Eigenschaften des Geräts und des Materials, das die PUF enthält, abhängt (d. h. von der einzigartigen internen Struktur der PUF, die durch zufällige Fertigungstoleranzen verursacht wird; diese Toleranzen sind in der Regel nicht reproduzierbar und liegen außerhalb der Kontrolle des PUF-Herstellers). Da PUFs durch Umwelteinflüsse bedingten Störungen unterliegen, liefern sie bei wiederholter Anfrage mit derselben Challenge leicht unterschiedliche Antworten. Dies lässt sich jedoch durch den Einsatz von FEC-Technologie (Fire Error Correction) mit einer sehr hohen Hamming-Distanz kompensieren. PUF-Architekturen (Publicly Identified Facility) werden auf einer Vielzahl von Plattformen implementiert, darunter FPGAs (Field-Programmable Gate Arrays), ASICs (Application-Specific Integrated Circuits), COTS-Produkte (Commercial Off-The-Shelf), Mikrocontroller, DSPs (Digital Signal Processors), ASSPs (Application-Specific Standard Products), SoCs (System-on-Chip), GPUs (Graphics Processing Units), ARM (Advanced RISC Machines), Mikroprozessoren und weitere. Innerhalb einer einzigen Plattform können unterschiedliche Technologien, wie beispielsweise CMOS-Knoten verschiedener Größenordnungen, zum Einsatz kommen. PUFs führen den Ansatz des „elektronischen Fingerabdrucks“ ein, wodurch die Identifizierung von den Eigenschaften des Geräts abhängt und nicht mehr auf einem geheimen Wissen beruht. Die moderne Informationssicherheit offenbart zunehmend ihre vielfältigen Facetten, wodurch ein stetig wachsendes Spektrum an Aufgaben bewältigt werden muss. Neben der herkömmlichen Kryptografie, die die Sicherheit von Daten gewährleistet, die in einem Netzwerk gespeichert oder übertragen werden, muss moderne Sicherheit einer wachsenden Zahl weiterer Anforderungen gerecht werden, wie etwa Vertrauen, Anonymität und die Vertraulichkeit von Handlungen. Frühe kryptografische Mechanismen, Protokolle und Methoden wurden für physisch gut geschützte Geräte entwickelt. Heutzutage ist jedoch die große Mehrheit der Geräte (RFID-/NFC-Tags mit und ohne Chips, intelligente Knoten in drahtlosen Sensornetzwerken (WSNs), Tablets usw.) leicht zugänglich, physisch ungeschützt und kann sich sogar in rauen Umgebungen befinden. Daher müssen moderne Sicherheitsprimitive (wie PUFs) gegen alle Arten von physischen Angriffen und Seitenkanalangriffen resistent sein und zudem kostengünstig und energieeffizient sein sowie die Einschränkungen tragbarer Computer und mobiler Kommunikationsgeräte mit begrenzter Akkukapazität und leistungsschwachen CPUs erfüllen. Die intrinsische Hardware-Sicherheit ist ein relativ neues Forschungsgebiet, das sich mit der sicheren Speicherung geheimer Schlüssel befasst. Die Generierung geheimer Schlüssel aus den intrinsischen Eigenschaften von Silizium, beispielsweise intrinsischen PUFs, erfordert keine dauerhafte Speicherung geheimer Schlüssel und der Schlüssel ist nur für eine minimale Zeitspanne im Bauelement vorhanden.

Das Feld erstreckt sich auf hardwarebasierte Sicherheitsprimitive und -protokolle wie Blockchiffren (z. B. AES, 3DES und IDEA) und Stromchiffren (z. B. OTP/Vernam), die in Hardware eingebettet sind und so die Sicherheit integrierter Schaltungen verbessern. Auf Anwendungsebene wächst das Interesse an Hardware-Sicherheit für RFID/NFC-Systeme und deren zugehörige Systemarchitekturen. Digitale Schlüssel werden traditionell in nichtflüchtigen Speichern (NVM) für kryptografische Anwendungen gespeichert. Digitale Schlüssel in NVMs haben sich jedoch als anfällig für invasive physische Angriffe erwiesen. Komplexe Manipulationsschutz- und Manipulationserkennungsmechanismen wurden in Hardware implementiert, um digitale Schlüssel in NVMs zu schützen. Dies erhöht jedoch den Stromverbrauch des Geräts erheblich und schränkt somit den Einsatz solcher Anti-Manipulationsmethoden für ressourcenbeschränkte Geräte wie Smartcards, RFID/NFC-Tags usw. ein. Zu den Eigenschaften von PUFs gehören Einzigartigkeit, Zuverlässigkeit und Unvorhersagbarkeit. Die PUF-Lösung von Intrinsic-ID ist für DesigWare ARC EM-Prozessoren verfügbar (http://www.synopsys.com/desigware). Sie ermöglicht es Entwicklern, einen eindeutigen „Geräte-Fingerabdruck“ aus dem standardmäßigen eingebetteten SRAM zu extrahieren. Dieser „Hardware-Fingerabdruck“ kann als Geräteidentifikator oder als geheimer/privater kryptografischer Schlüssel verwendet werden. Im letzteren Fall wird ein sicherer Schlüsselschutz geschaffen, ohne dass NVM (nichtflüchtiger Speicher) oder ein dedizierter Sicherheitskern erforderlich ist.

Das Feld erstreckt sich auf hardwarebasierte Sicherheitsprimitive und -protokolle wie Blockchiffren (z. B. AES, 3DES und IDEA) und Stromchiffren (z. B. OTP/Vernam), die in Hardware eingebettet sind und so die Sicherheit integrierter Schaltungen verbessern. Auf Anwendungsebene wächst das Interesse an Hardware-Sicherheit für RFID/NFC-Systeme und deren zugehörige Systemarchitekturen. Digitale Schlüssel werden traditionell in nichtflüchtigen Speichern (NVM) für kryptografische Anwendungen gespeichert. Digitale Schlüssel in NVMs haben sich jedoch als anfällig für invasive physische Angriffe erwiesen. Komplexe Manipulationsschutz- und Manipulationserkennungsmechanismen wurden in Hardware implementiert, um digitale Schlüssel in NVMs zu schützen. Dies erhöht jedoch den Stromverbrauch des Geräts erheblich und schränkt somit den Einsatz solcher Anti-Manipulationsmethoden für ressourcenbeschränkte Geräte wie Smartcards, RFID/NFC-Tags usw. ein. Zu den Eigenschaften von PUFs gehören Einzigartigkeit, Zuverlässigkeit und Unvorhersagbarkeit. Die PUF-Lösung von Intrinsic-ID ist für DesigWare ARC EM-Prozessoren verfügbar (http://www.synopsys.com/desigware). Sie ermöglicht es Entwicklern, einen eindeutigen „Geräte-Fingerabdruck“ aus dem standardmäßigen eingebetteten SRAM zu extrahieren. Dieser „Hardware-Fingerabdruck“ kann als Geräteidentifikator oder als geheimer/privater kryptografischer Schlüssel verwendet werden. Im letzteren Fall wird ein sicherer Schlüsselschutz geschaffen, ohne dass NVM (nichtflüchtiger Speicher) oder ein dedizierter Sicherheitskern erforderlich ist.

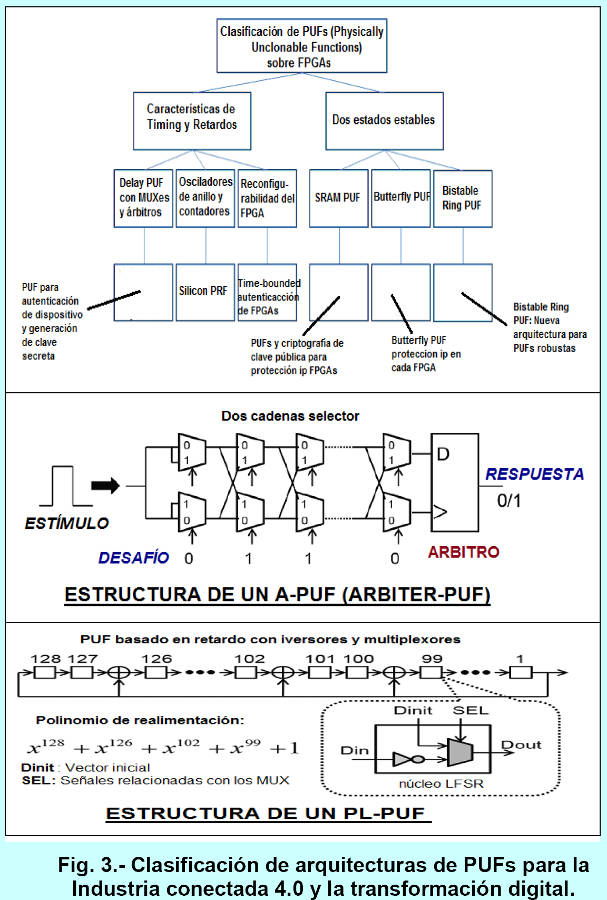

Taxonomie der PUF-Architekturklassifizierungen für die vernetzte Industrie 4.0.

Taxonomie der PUF-Architekturklassifizierungen für die vernetzte Industrie 4.0.

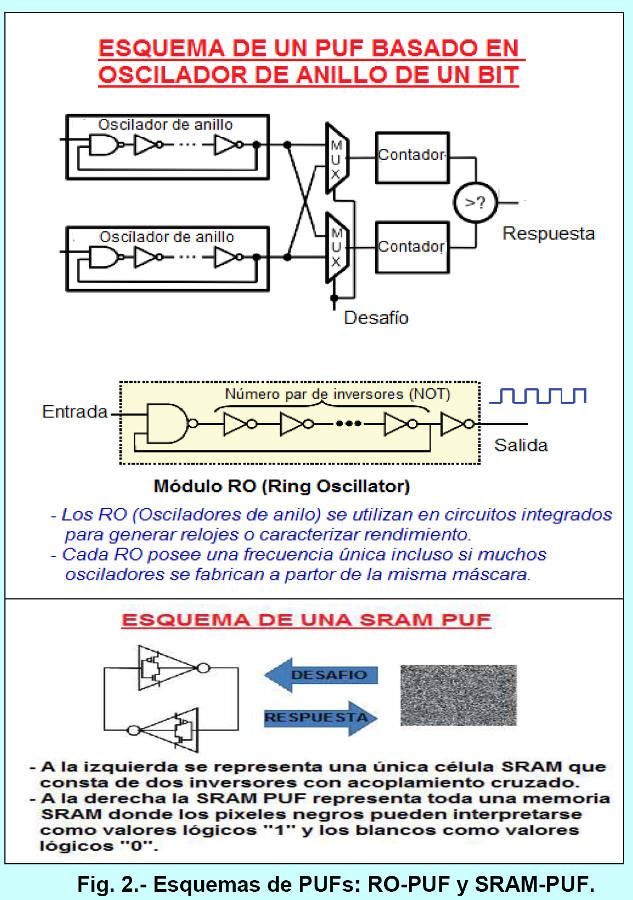

Im Laufe der Geschichte wurden verschiedene Methoden zur Synthese von PUFs entwickelt, von der Messung der Verzerrung reflektierten Lichts bis hin zur Nutzung von Fertigungstoleranzen zwischen Chips (physikalische Eigenschaften der verwendeten Materialien). PUFs, die auf konventionellen mikroelektronischen Schaltungen basieren, wie z. B. RO-PUFs (Ringoszillator-PUFs), A-PUFs (Arbiter-PUFs) und SRAM-PUFs, nutzen unkontrollierte Prozessschwankungen in der CMOS-Fertigungstechnologie (Complementary Metal-Oxide-Semiconductor). Auch die im Jahr 2000 vorgeschlagenen siliziumbasierten Identifikationsschaltungen lassen sich als PUFs klassifizieren, da sie ebenfalls die Zufälligkeit innerhalb des Hardwarebauelements zur Generierung eines geheimen Schlüssels nutzen. Die nächste Generation von PUFs wird derzeit mithilfe neuartiger nanoelektronischer und Quantenbauelemente realisiert. Nanotechnologien wie PCM (Phasenwechselspeicher), STT-MRAM (Spin-Transfer-Torque-Magnetspeicher), CNFETs (Kohlenstoffnanoröhren-Feldeffekttransistoren) und Memristoren (auch bekannt als bipolarer Memristor, memristives Bauelement oder RRAM; eine Abkürzung für „Speicher“ und „Widerstand“, ein Begriff, der 1971 von Leon Chua geprägt wurde. Ein Beispiel ist die memristorbasierte Nano-Crossbar-PUF-Architektur, kurz mrPUF) weisen aufgrund von Fertigungstoleranzen (z. B. Dicke, Querschnittsfläche oder Dotierungsprofil) eine höhere inhärente Zufälligkeit auf. Im Quantenbereich wird der QR-PUF (Quanten-Auslese-PUF) mithilfe eines Quantenzustands untersucht. Zu den am häufigsten verwendeten PUF-Architekturen, unter Berücksichtigung ihrer Zusammensetzung, Trägerstruktur und ihres Aufbaus, gehören:

1) Silizium-PUFs und Nicht-Silizium-PUFs, einschließlich Kristall-PUFs und Timing-PUFs.

2) Ringoszillatorbasierte PUFs (RO-PUFs). Diese basieren auf den Frequenzdifferenzen mehrerer Ringoszillatoren. Ein Ringoszillator ist eine Kaskadenschaltung einer geraden Anzahl von NOT-Inverter-Gattern. Aufgrund der geraden Anzahl an Gattern erzeugt er ein kontinuierlich veränderliches oder oszillierendes Signal. Als Kombination von Schaltungen kann der RO-PUF auf einem Siliziumchip als FPGA oder ASIC (anwendungsspezifischer integrierter Schaltkreis) realisiert werden. Abhängig von der Anzahl der verwendeten Inverter-Gatter sowie der Laufzeitverzögerung jedes einzelnen Inverters kann die Ausgangsfrequenz eines RO-PUFs von der eines anderen abweichen. Der RO-PUF zählt aufgrund seiner hohen Zuverlässigkeit zu den führenden mikroelektronischen PUFs.

3) Optische PUFs (O-PUFs). Sie bestehen aus einem transparenten Material, dem während der Herstellung zahlreiche lichtstreuende Partikel zufällig beigemischt werden. Beim Auftreffen eines Laserstrahls auf den PUF entsteht ein zufälliges Punktmuster. Position und Winkel des Lasers stellen die Herausforderung dar, während das Punktmuster aufgezeichnet, quantisiert und kodiert wird, um die Antwort des PUF zu erzeugen. Ein optischer PUF wird hergestellt, indem ein transparentes Material zufällig mit lichtstreuenden Partikeln beschichtet wird. Ein Laserstrahl wird auf das Material fokussiert, und das entstehende Muster wird aufgezeichnet. Das Bild wird verarbeitet und bildet die Antwort des PUF.

4) APUF (Arbiter-PUF). Diese verwenden FPGAs (Field-Programmable Gate Arrays) und basieren auf dem Laufzeitvergleich zweier symmetrischer Verzögerungsleitungen. Sie bestehen aus Selektionsketten, in denen die Signaleingänge an den Selektoren, die die Herausforderung bilden, ausgewählt werden. Das Signal, das von den Arbitern ausgegeben wird, ist die Antwort. Erreicht das obere Signal den unteren Arbiter vor diesem, ist die Antwort „eins“, andernfalls „null“. Der Pfad der Selektorketten und die Verzögerungen, die zwischen zwei Signalen unterscheiden, werden durch die Herausforderung bestimmt, sodass die Antwort eine Funktion der Herausforderung ist. Da die Geschwindigkeiten der beiden Signale in den Selektorketten durch Gerätevariationen beeinflusst werden, ist die Antwort auf eine bestimmte Herausforderung nicht immer für verschiedene APUFs gleich. Daher stellt ein Satz von Challenge-Response-Paaren (CRPs) eines APUF chipspezifische Information dar, die zur Authentifizierung dieses Chips verwendet werden kann.

5) PL-PUFs (Pseudo-LFSR-PUFs). Diese verwenden FPGAs. Es handelt sich um verzögerungsbasierte PUFs mit einer Struktur, die einem LFSR (Linear-Feedback-Shift-Register) ähnelt und sogar ein nichtreduzierbares Rückkopplungspolynom wie x<sup>128</sup>+x<sup>126</sup>+x<sup>102</sup>+x<sup>99</sup>+1 verwendet. Ein PL-PUF besteht nicht aus Schieberegistern, sondern aus kombinatorischer Logik, bestehend aus Multiplexern und Inverter an jedem Knoten.

6) SRAM-PUFs. Sie basieren auf der Metastabilität eines kreuzgekoppelten Bauelements. Es besteht aus zwei kreuzgekoppelten Inverter und zwei zusätzlichen Transistoren für externe Verbindungen, insgesamt also sechs Transistoren. Es eignet sich schnell für die kurzfristige Datenspeicherung.

Eine weitere Klassifizierung von PUFs, die zusätzliche operative Aspekte berücksichtigt, ist:

Eine weitere Klassifizierung von PUFs, die zusätzliche operative Aspekte berücksichtigt, ist:

1) Rekonfigurierbare PUFs (RPUFs). Diese können ihre Antwort auf dieselbe Herausforderung ändern, anstatt ein statisches Challenge-Response-Verhalten zu zeigen. Sie sind nützlich für Anwendungen wie den Widerruf oder die Aktualisierung von Geheimnissen. Sie weisen folgende Eigenschaften auf: (i) Die CRPs sind nach der Rekonfiguration unvorhersehbar, selbst wenn sie vor der Rekonfiguration bekannt waren. (ii) Die Sicherheitseigenschaften von RPUFs bleiben nach der Rekonfiguration erhalten. (iii) Die Rekonfiguration ist unkontrollierbar und basiert daher nicht auf der Aktualisierung versteckter Parameter oder Geräte. RPUFs ermöglichen die Erweiterung des regulären Challenge-Response-Verhaltens eines PUF um eine zusätzliche Operation, die Rekonfiguration genannt wird. Diese Rekonfiguration bewirkt eine teilweise oder vollständige zufällige und irreversible Änderung des Challenge-Response-Verhaltens des PUF, wodurch ein neuer PUF entsteht. Es gibt verschiedene Implementierungen von RPUFs, bei denen der Rekonfigurationsmechanismus eine tatsächliche physikalische Rekonfiguration der Zufälligkeit im PUF darstellt. Eine Erweiterung eines O-PUF besteht in der Verwendung eines leistungsstärkeren Laserstrahls, der eine zufällige Neuanordnung der optischen Streuung bewirkt und so ein neues Challenge-Response-Verhalten zur Folge hat.

2) CPUFS (Controlled PUFs). Diese verwenden einen robusten PUF als Baustein, ergänzen ihn jedoch um eine Kontrolllogik. Diese Logik verhindert, dass Challenges frei an den PUF gerichtet werden und seine Antworten direkt ausgelesen werden können. Dadurch lassen sich Spoofing-Angriffe verhindern. Können die Ausgaben des eingebetteten robusten PUF jedoch direkt untersucht werden, ist es möglicherweise möglich, den robusten PUF zu spoofen und das Protokoll des Controlled PUF zu brechen. Ein PUF gilt als CPUF, wenn der Zugriff nur über einen Algorithmus möglich ist, der physisch und untrennbar mit dem PUF verbunden ist. Der Versuch, diese Verbindung zu unterbrechen, sollte zur Zerstörung des PUF führen. Ein CPUF kombiniert einen PUF mit einer weiteren kryptografischen Primitive. Einige Vorteile der Umwandlung eines PUF in einen CPUF sind: (i) Eine kryptografische Hashfunktion zur Generierung der PUF-Herausforderungen kann Angriffe mit gewählter Herausforderung verhindern, d. h. Modellierungsangriffe erschweren. (ii) Ein Fehlerkorrekturalgorithmus, der auf die PUF-Messungen angewendet wird, macht die endgültige Antwort deutlich zuverlässiger und reduziert die Wahrscheinlichkeit eines Ein-Bit-Fehlers in der Antwort praktisch auf null. (iii) Eine kryptografische Hashfunktion, die auf die fehlerkorrigierten Ausgaben angewendet wird, trennt effektiv die Verbindung zwischen den Antworten und den physikalischen Details der PUF-Messung. Dies erschwert Modellierungsangriffe erheblich. Beim Hashen einer PUF-Antwort ist die Fehlerkorrektur unerlässlich, da jede noch so kleine Abweichung von der Antwort zu einem völlig unabhängigen Hash-Ergebnis führt. (iv) Die Hashfunktion, die die PUF-Herausforderungen generiert, kann zusätzliche Eingaben verarbeiten, wodurch ein PUF mehrere Eigenschaften aufweisen kann. Dies kann wünschenswert sein, wenn der PUF in datenschutzsensiblen Anwendungen verwendet wird.

3) POKs (Physically Obfuscated Keys). Die einzige Voraussetzung für einen POK ist, dass der Schlüssel dauerhaft in physischer Form und nicht digital gespeichert wird. Dies erschwert es Angreifern, den Schlüssel durch einen Sondierungsangriff zu ermitteln. Darüber hinaus sollte ein invasiver Angriff auf das Gerät, auf dem der Schlüssel gespeichert ist, diesen zerstören und seine weitere Verwendung unmöglich machen, wodurch ein Manipulationsnachweis erbracht wird. POKs und PUFs sind sehr ähnliche Konzepte, und POKs können aus PUFs (mit Manipulationsnachweis) erstellt werden und umgekehrt.

4) PUF-Rekombination. Rekombination kann auf ein System angewendet werden, das verschiedene Arten von PUFs enthält. In der Gentechnik bezeichnet Rekombination den Prozess, bei dem genetisches Material (in diesem Fall Silizium-PUF-Schaltungen) neu angeordnet und verbunden wird, um anderes genetisches Material zu erzeugen. Zu seinen Vorteilen zählt seine Eignung als hervorragendes Material für die Schlüsselerzeugung und Authentifizierung. Es ermöglicht einen erweiterten Challenge-Response-Raum (z. B. 2 hoch 128), erhöht die Stabilität in verschiedenen Umgebungen, reduziert die Komplexität der Schlüsselerzeugung und ist auf FPGAs und ASICs realisierbar. Dadurch werden die Risiken von ASIC-Implementierungen durch Prototyping und schnelle FPGA-Emulation minimiert und Schutz für FPGA- und ASIC-basierte Systeme und Geräte geboten.

Je nach Anzahl der von einem PUF erzeugbaren Challenge-Response-Paare (CRPs) lassen sich PUFs in zwei Hauptkategorien einteilen:

1) Schwache PUFs. Diese unterstützen nur eine geringe Anzahl von CRPs, sodass diese innerhalb kürzester Zeit vollständig ausgelesen werden können, sobald ein Angreifer vollen physischen Zugriff auf den PUF erlangt hat. Ein schwacher PUF ist durch zwei Eigenschaften definiert: (i) Er kann weder geklont noch physisch dupliziert werden. (ii) Die Anzahl der CRPs ist begrenzt und hängt linear oder polynomiell von der Anzahl der Bits in der Challenge ab. Beispiele für schwache PUFs sind SRAM-PUF, Coating-PUF, Butterfly-PUF usw. Sie werden für Schlüsselspeicheranwendungen verwendet. Beispielsweise wird ein eindeutiger interner geheimer Schlüssel aus den Antworten mehrerer schwacher PUFs gewonnen.

2) Robuste PUFs (manchmal auch PRFs, Physical Random Functions, genannt) zeichnen sich durch drei Eigenschaften aus: (i) Sie sind unmöglich zu klonen oder physisch zu duplizieren. (ii) Sie unterstützen eine sehr große Anzahl von CRPs, sodass ein Angreifer innerhalb realistischer Zeit keinen Brute-Force-Angriff durchführen kann, idealerweise demonstriert durch eine exponentielle Anzahl von CRPs. (iii) Sie sind resistent gegen Modellierungsangriffe, da sie eine polynomische Anzahl gewählter CRPs bereitstellen, sodass ein Angreifer die Antwort einer PUF auf eine zufällig ausgewählte, ungenutzte Herausforderung nicht vorhersagen kann. Beispiele für robuste PUFs sind Optical-PUF, XOR-PUF usw. Anwendungen dieser PUFs sind unter anderem Schlüsselaustausch, Identifizierung, Authentifizierung, transcorded transfer, Null Knowledge Proofs, SMPC (Secure Multi-Party Computation) usw.

Cybersicherheit und Datenschutz (Schutz vor Angriffen jeglicher Art) müssen in den vier wichtigsten Aspekten von Industrie 4.0 höchste Priorität haben: vertikale Integration (hohe Flexibilität, keine Losgrößen), der Mensch als zentraler Wertschöpfungstreiber (Systeme orientieren sich an den Bedürfnissen der Nutzer, Mitarbeiterentwicklung und Massenindividualisierung), horizontale Integration (globale Wertschöpfungsketten) und konsistentes Engineering (Systementwicklung über den gesamten Lebenszyklus mit digitaler Produktion). Industrie 4.0 hat durch das industrielle Internet der Dinge (IIoT) die Büchse der Pandora für Cyberangriffe aller Art geöffnet – von konventionellen bis hin zu hochentwickelten Angriffen wie APT-basierten Attacken. Cybersicherheit und Datenschutz haben daher höchste Priorität. Ein wichtiges Werkzeug hierfür sind physikalisch nicht klonbare Funktionen (PUFs). Das Sandia National Laboratory vermarktet eine Technologie namens SecuritySeal, die kryptografische Cybersicherheitstechniken auf Basis von PUFs nutzt, um physische Objekte vor Betrug zu schützen, beispielsweise vor der Fälschung radioaktiver Materialien oder Arzneimittel in Behältern. Cyber-Physical Systems (CPS) sind ein zunehmend in verschiedenen Technologien eingesetztes Rechenparadigma und bilden die Grundlage von Industrie 4.0. Für zuverlässige CPS sind Mechanismen erforderlich, die die Integrität und Authentizität dieser Systeme gewährleisten. Auf Halbleitertechnologien basierende PUFs (Polymer-Ultrawide Fibers) bieten sich als hochgeeignete Lösung an, um Verbindungen zwischen der digitalen und der analogen Welt herzustellen und CPS in der Avionik, autonomen Fahrzeugen, Fabrikmaschinen, Produktionssystemen, Industriezweigen, kritischen Infrastrukturen (mit und ohne SCADA), im Finanzwesen und weiteren Bereichen zu schützen. Zu den Aufgaben sicherer Hardwarekomponenten wie PUFs gehören: Schlüsselspeicherung, asymmetrische Kryptografie (Signatur und Verschlüsselung, z. B. basierend auf ECC/RSA-CRT), Sitzungsschlüsselgenerierung, Zufallszahlengenerierung, Überprüfung von Zugriffsrechten und Integrität, sichere Datenspeicherung, Schutz vor Hardwareangriffen, Zertifizierung/Attestierung usw. In Mobiltelefonen finden sich verschiedene sichere Hardwarekomponenten: SIM-Karten, eSIMs, Sicherheitschips, sichere SD-Karten usw. Im März 2007 führte das Idaho National Laboratory des US-Energieministeriums ein Experiment namens Aurora durch, um zu demonstrieren, wie ein Cyberangriff physische Komponenten eines Stromnetzes zerstören kann. Das Experiment nutzte eine Software, die einen Stromkreis in einem Dieselgenerator schnell öffnete und schloss, was zu einer Explosion führte. Diese Schwachstelle wurde als Aurora-Schwachstelle bekannt und kann daher von Cyberangriffen ausgenutzt werden. Das US-Heimatschutzministerium (DHS) arbeitet seitdem mit der Elektroindustrie zusammen, um zukünftige Bedrohungen dieser Art zu verhindern. Aktuell gibt es bereits autonom fahrende Saugroboter, die per Smartphone ferngesteuerte Videoüberwachung ermöglichen und dadurch anfällig für Hackerangriffe sind. Noch gefährlicher sind die neuesten Spielzeuge und Babyphone der nächsten Generation, wie zum Beispiel die Puppen „My Friend Cayla“, „Hello Barbie“, der „Fisher-Price Smart Toy Bear“ und der intelligente Roboter „i-Que“, die sich mit dem Internet verbinden, Gespräche mit Kindern aufzeichnen und eine gewisse Ferninteraktion über das Internet ermöglichen (z. B. vom Bären aufgenommene Fotos).

AUTOR:

Prof. Dr. Javier Areitio Bertolín,

Professor an der Fakultät für Ingenieurwissenschaften der Universität Deusto.

Direktor der Forschungsgruppe Netzwerke und Systeme.

LITERATURVERZEICHNIS.

- Areitio, J. „Information Security: Networks, Computing and Information Systems“. Cengage Learning-Paraninfo. 2017.

- Areitio, J. „Exploration and cross-cutting analysis of the IoE from the perspective of cybersecurity and privacy“. Conectrónica Magazine. Nr. 193. Februar 2016.

- Areitio, J. „Systematic classification of cyberattacks and approaches to assessing cyber threats in IoE ecosystems“. Conectrónica Magazine. Nr. 199. September 2016.

- Areitio, J. „Identification, exploration and classification of cyberattack surfaces at the data and code level in the IoE“. Conectrónica Magazine. Nr. 200. Oktober 2016.

– Intrinsic-ID, ein Spin-off von Philips Electronics, stellt PUFs für eingebettete Authentifizierung her, URL: https://www.intrinsic-id.com/products/

– Wachsmann, C. und Sadeghi, A. R.: „Physically Unclonable Functions (PUFs): Applications, Models and Future Directions“. Morgan & Claypool Publishers. 2015.

– Verayo, gegründet 2005, stellt PUF-Technologie her, URL: http://www.verayo.com/

– Mukhopadhyay, D. und Chakraborty, R. S.: „Hardware Security: Design, Threats and Safeguards“. Chapman and Hall/CRC. 2014.

– RAMI 4.0 (Referenzarchitekturmodell für Industrie 4.0) vom ZVEI (Verband der Elektro- und Elektronikindustrie).

– Tehranipoor, M. und Wang, C.: „Introduction to Hardware Security and Trust“. Springer. 2012.

– Patterson, DG: „Physical Security Protection Systems Implementation and Operation“. CRC Press. 2016.

– Bohm, C. und Hofer, M.: „Physical Unclonable Functions in Theory and Practice“. Springer-Verlag. 2013.

– Sadeghi, AR und Naccache, D: „Towards Hardware-Intrinsic Security: Information Security and Cryptography“. Springer. Berlin. 2010.

– Tehranipoor, M., Salmani, H. und Zhang, X.: „Integrated Circuit Authentication: Hardware Trojans and Counterfeit Detection“. Springer. 2014.

– Qu, G. und Potkonjak, M. „Intellectual Property Protection in VLSI Designs. Theory and Practice“. Kluwer. 2003.

– Dittmann, A., Heinrichs, B., Hellwig, S. und Seewald, M. G. „Internet of Things / Internet of Everything: A Practical Architecture Approach“. Cisco Press. 2016.

– Sadeghi, A.-R. und Naccache, D. „Towards Hardware-Intrinsic Security: Information Security and Cryptography“. Springer-Verlag.

– Projekt zu PUFs: Europäisches H2020-Projekt HECTOR. URL: http://www.hector-project.eu/

.