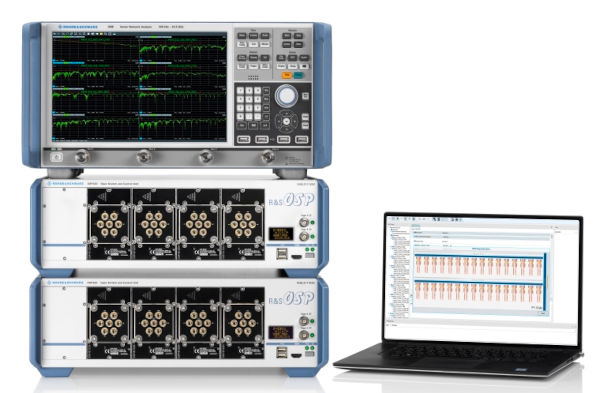

A configurator allows users to select and deselect test items from different lanes to more flexibly meet customer needs and preferences in R&D and verification testing. At the end of the automated measurement, a test report with a "pass/fail" verdict is generated. It also includes a process for de-embedding the test adapter, as required by PCIe testing specifications. Each PCIe link consists of 1, 2, 4, 8, or 16 lane pairs, and each lane pair comprises a differential TX lane and a differential RX lane. With 8 lane pairs in an x8 configuration, a PCIe 6.0 cable can achieve transfer speeds of up to 64 GB/s. Manually verifying compliance of high-speed interconnects is a laborious and error-prone task. A total of 256 four-port measurements are required for all link connections and all crosstalk and forward crosstalk paths within the cable. When using a conventional four-port vector network analyzer, the VNA must be reconnected for each four-port measurement and the unmeasured lanes must be properly terminated.

Since certain instances of exceeding the limit mask are not critical to the overall behavior of the PCIe 5.0/6.0 system, pass/fail verdicts are based on metrics such as Integrated Return Loss (iRL) and Component Contribution Integrated Crosstalk Noise (ccICN). These are defined in the PCI-SIG specification and must be calculated from the S-parameter results, thus requiring significant post-processing. Calibration and characterization of the test adapters and de-embedding present additional challenges for engineers.

Due to their importance to PCIe systems, PCI-SIG is defining standardized cables for internal (within a chassis) and external (chassis-to-chassis) applications, including corresponding electrical requirements for mated cable assemblies and mated cable connectors at speeds of 32 GT/s and 64 GT/s. The R&S ZN-run-K440 will also cover these PCIe tests once they have been standardized.