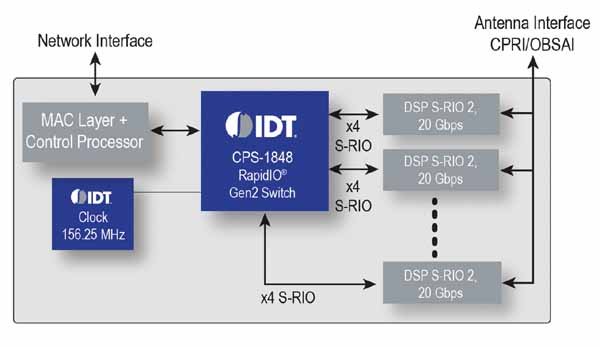

The first architecture, shown in Figure 1, uses one or more application-specific integrated circuits (ASICs) or field-programmable gate arrays (FPGAs) to receive and transmit antenna data, typically via the Common Public Radio Interface (CPRI) or the Open Base Station Architecture Initiative (OBSAI), a common antenna interface standard. This is used when the PHY (physical layer protocol) layer of the wireless protocol is implemented on the ASIC/FPGA. The data is then transferred via S-RIO to a set of digital signal processors (DSPs) for wireless protocol processing at the Media Access Control (MAC) sublayer. Higher-level MAC processing is performed on the control processor (CP). The CP is used for Quality of Service (QoS) and numerous other management functions on the baseband card. Furthermore, it typically handles network access via Gigabit Ethernet links and implements security for public network access. Additionally, some architectures feature a centralized network interface where the central processing unit (CP) of each baseband card can communicate with the network interface card that implements the public network access security function.

By using an FPGA in this architecture, the base station is fully scalable and software-programmable. It can be described as a software-configurable base station. System designers would have the option to increase or decrease the size of the FPGA, as well as add or remove DSPs, to obtain a larger or smaller base station capable of serving a greater or lesser number of subscribers. Similarly, for the MIMO algorithm, designers could group users into larger or smaller groups, which would require greater or lesser processing capacity from the FPGA and the DSPs.

In the second architecture, shown in Figure 2, neither FPGAs nor ASICs are used in the antenna data path; instead, all antenna traffic is sent to all DSPs in the system. This is a distributed architecture. Each DSP receives the antenna data and uses only what it needs to serve its assigned users. Once sample processing is complete in the DSPs, the data packets can be sent via S-RIO to the control processor and to the network. Similarly, there is significant control traffic between the control processor and the DSPs for QoS and management functions specific to each user. Serial RapidIO is ideal for architectures that utilize logic layer features, such as direct memory transactions and/or RapidIO Messaging, which is an efficient way to transmit long messages of up to 4 KB. RapidIO Messaging is a "push" architecture and offers the system with the lowest latency compared to other protocols. The switching latency of Serial RapidIO is also minimal—approximately 100 ns—and establishes efficient data transfer between digital signal processors. Furthermore, this architecture is scalable and can also be described as a software-configurable base station.

the second architecture, shown in Figure 2, neither FPGAs nor ASICs are used in the antenna data path; instead, all antenna traffic is sent to all DSPs in the system. This is a distributed architecture. Each DSP receives the antenna data and uses only what it needs to serve its assigned users. Once sample processing is complete in the DSPs, the data packets can be sent via S-RIO to the control processor and to the network. Similarly, there is significant control traffic between the control processor and the DSPs for QoS and management functions specific to each user. Serial RapidIO is ideal for architectures that utilize logic layer features, such as direct memory transactions and/or RapidIO Messaging, which is an efficient way to transmit long messages of up to 4 KB. RapidIO Messaging is a "push" architecture and offers the system with the lowest latency compared to other protocols. The switching latency of Serial RapidIO is also minimal—approximately 100 ns—and establishes efficient data transfer between digital signal processors. Furthermore, this architecture is scalable and can also be described as a software-configurable base station.

With this architecture, designers can not only define larger or smaller base stations to serve more or fewer users, but they can also comply with different wireless standards using the same architecture. Simply changing the software transforms the architecture into a common platform across different standards.

In the architectures shown in Figures 1 and 2, the S-RIO data flows differ significantly. Similarly, the same architecture that would comply with different wireless standards, such as WCDMA and LTE, would require a

different S-RIO data flow. For this reason, it is advisable to model S-RIO traffic scenarios within the system to ensure that the speed and size of each link are adequate to run the necessary algorithm without exceeding the time budgeted for each standard. S-RIO offers link widths and speeds of x1, x2, and x4, respectively, and from 1.25 to 6.25 Gbps. Figures 1 and 2 show x4 S-RIO links, but some systems can operate with narrower links, if appropriate, depending on the number of users served and the characteristics of each DSP involved.

Serial RapidIO is the only interconnect technology defined for a distributed set of processors arranged in any topology with easy routing and scalability. Its simplified approach to packet routing, based on the destination ID field, allows software implementers to easily discover new nodes in a system or redistribute traffic in case of processing errors. Serial RapidIO is scalable while maintaining the same software programming model without the memory mapping problems common in other protocols. No other protocol can make the two architectures described above software-programmable base stations.

Serial RapidIO is the only interconnect technology defined for a distributed set of processors arranged in any topology with easy routing and scalability. Its simplified approach to packet routing, based on the destination ID field, allows software implementers to easily discover new nodes in a system or redistribute traffic in case of processing errors. Serial RapidIO is scalable while maintaining the same software programming model without the memory mapping problems common in other protocols. No other protocol can make the two architectures described above software-programmable base stations.

Author: Stephane Gagnon, Director of Product Management at Serial RapidIO, IDT

About the author:

Stephane Gagnon, Director of Product Management, joined IDT in August 2000. Stephane has held many different positions, including systems architect, director of Systems Engineering and Manufacturing Testing, and director of Strategic Marketing. For the past ten years, Stephane has also collaborated with the Professional Association's RapidIO Technical Working Group. He currently chairs the Professional Association's Steering Committee. Before joining IDT, Stephane worked for one year as an Applications Engineer (FAE) at Motorola and for seven years as a hardware systems designer at Nortel Networks.